Aaye ohun elo

1. Ga-iyara ese Circuit

2. Makirowefu awọn ẹrọ

3. Ga iwọn otutu ese Circuit

4. Awọn ẹrọ agbara

5. Kekere agbara ese Circuit

6. MEMS

7. Low foliteji ese Circuit

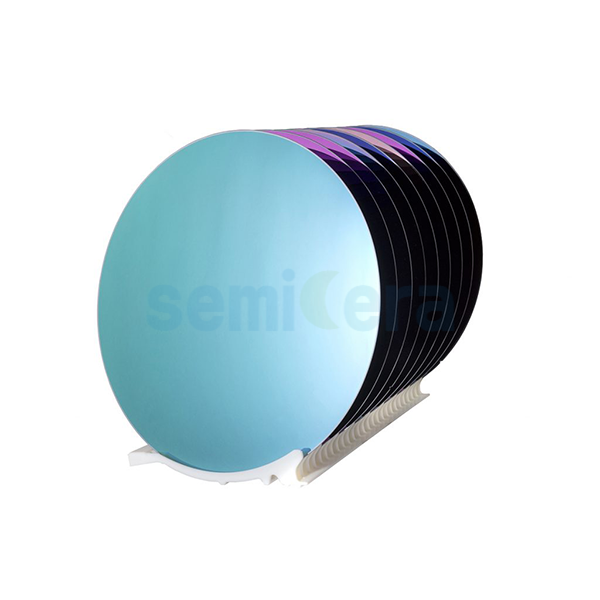

| Nkan | Ariyanjiyan | |

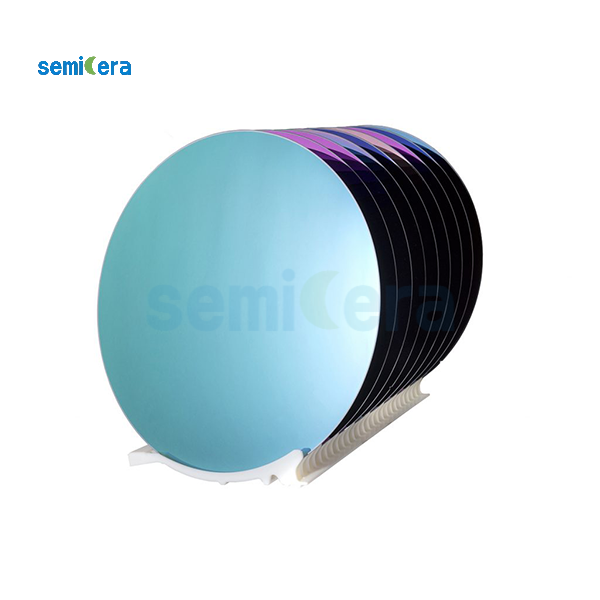

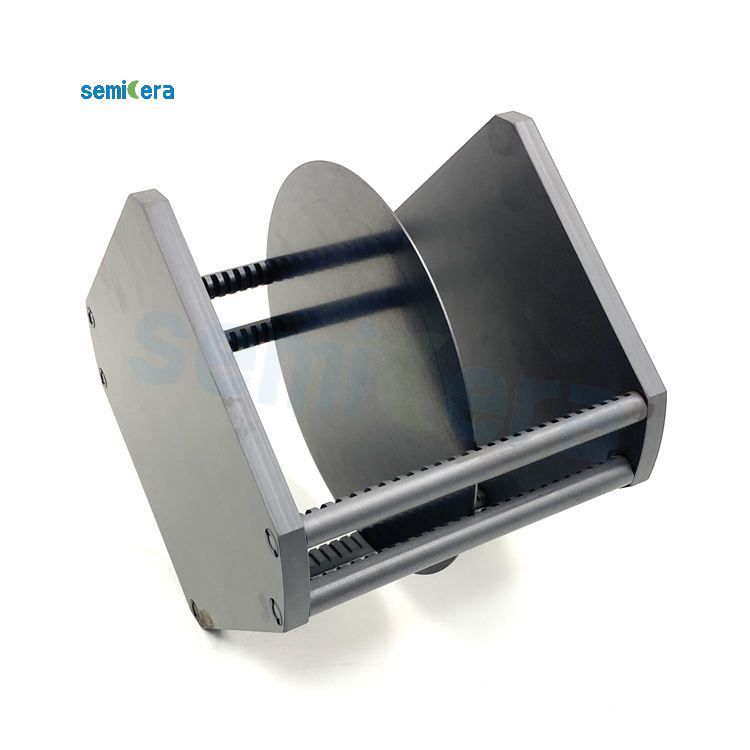

| Lapapọ | Wafer Opin | 50/75/100/125/150/200mm ± 25um |

| Teriba / Warp | <10um | |

| Awọn patikulu | 0.3um <30ea | |

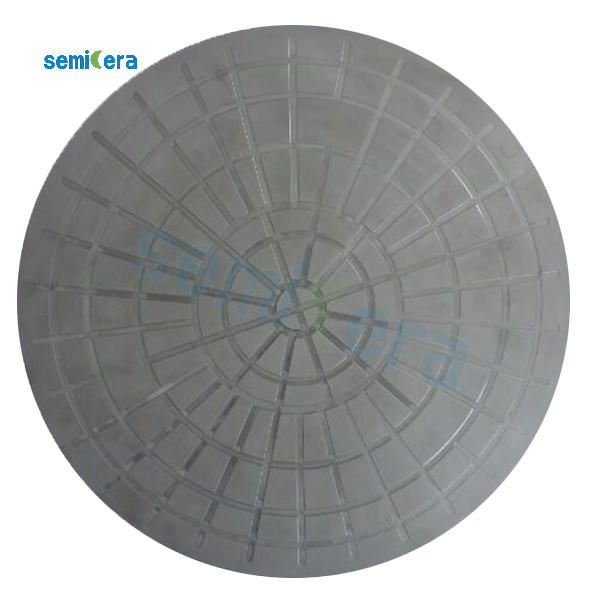

| Alapin / ogbontarigi | Alapin tabi ogbontarigi | |

| Iyasoto eti | / | |

| Layer ẹrọ | Ẹrọ-Layer Iru/Dopant | N-Iru / P-Iru |

| Ohun elo-Layer Iṣalaye | <1-0-0> / <1-1-1> / <1-1-0> | |

| Ohun elo-Layer Sisanra | 0.1 ~ 300um | |

| Resistivity Layer ẹrọ | 0.001 ~ 100,000 ohm-cm | |

| Ẹrọ-Layer patikulu | <30ea@0.3 | |

| Ẹrọ Layer TTV | <10um | |

| Ipari ẹrọ Layer | Didan | |

| Apoti | Sisanra Oxide Gbona | 50nm(500Å)~15um |

| Mu Layer | Mu Wafer Iru / Dopant | N-Iru / P-Iru |

| Mu Wafer Iṣalaye | <1-0-0> / <1-1-1> / <1-1-0> | |

| Mu Wafer Resistivity | 0.001 ~ 100,000 ohm-cm | |

| Mu Wafer Sisanra | >100um | |

| Mu Wafer Pari | Didan | |

| SOI wafers ti awọn pato ibi-afẹde le jẹ adani ni ibamu si awọn ibeere alabara. | ||